## Update on Address Hashing and Hash Conflicts in Intel Xeon Scalable Processors

John D. McCalpin, PhD mccalpin@tacc.utexas.edu IXPUG BOF SC18

THE UNIVERSITY OF TEXAS AT AUSTIN

**TEXAS ADVANCED COMPUTING CENTER**

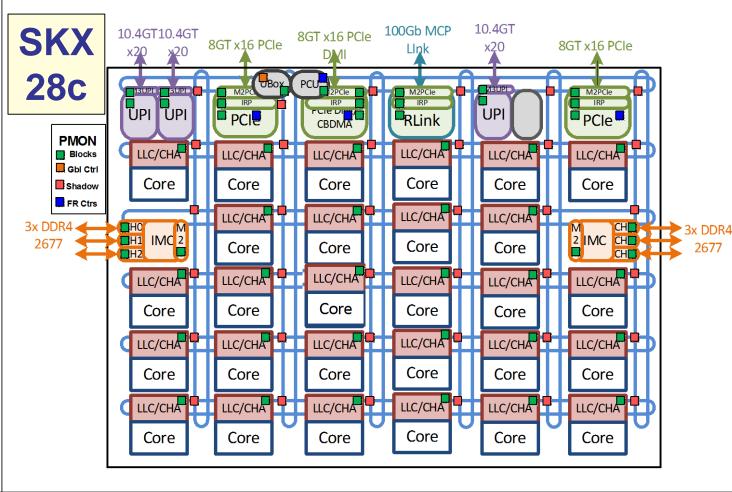

Intel Xeon Scalable Processors:

Each "Core" box includes a core + private L1 and L2 caches

Each cache line address is mapped to exactly one LLC/CHA by an undocumented hash

Figure 1-1 from Intel document 336274-001

Cache lines are distributed fairly uniformly *across* the LLC/CHA boxes...

But not always uniformly *within* each LLC/CHA box

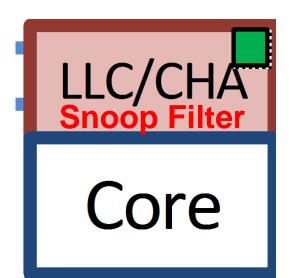

The "**Snoop Filter**" in the LLC/CHA box tracks lines held in L1/L2 caches

When a new Snoop Filter entry is needed, the cache line tracked by the replaced entry must be evicted from all other L1 and L2 caches in the chip

If the line is in active use, it will immediately be reloaded by that other core

This will cause another line to be evicted, causing another line to be evicted....

Classic case of "thrashing"

LLC/CHA Snoop Filter

Core

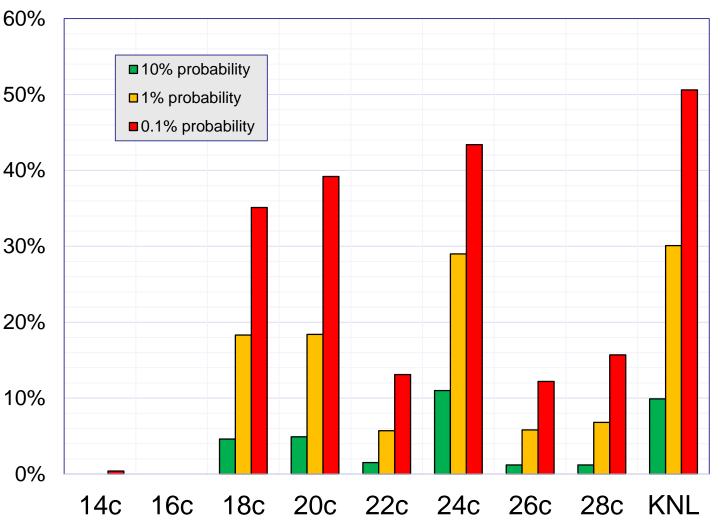

Average Snoop6Filter Eviction Ratiofor repeated arrayread test on 2 MiBpages

Tests run on: 14c Xeon Gold 6132 16c Xeon Gold 6142 18c Xeon Gold 6150 20c Xeon Gold 6150 20c Xeon Gold 6152 24c Xeon Platinum 8160 26c Xeon Platinum 8170 28c Xeon Platinum 8180 KNL Xeon Phi 7250

Thanks: Dell Customer Solutions Center!

## John D. McCalpin, PhD mccalpin@tacc.utexas.edu

## 512-232-3754

For more information: <u>www.tacc.utexas.edu</u>