## The Analysis of Inter-Process Interference on a Hybrid Memory System

#### <u>Satoshi Imamura</u> and Eiji Yoshida Fujitsu Laboratories Ltd., Japan

IXPUG HPC Asia 2020, January 17, 2020

## Intel® Optane<sup>™</sup> DC Persistent Memory (DCPM) Fujitsu

#### First persistent memory product

- Connected to DIMM slots

- Byte-addressable

- Non-volatile

Larger capacity than DRAM

128, 256, 512 GB per DIMM

https://www.intel.co.jp/content/www/jp/ja/architectureand-technology/optane-dc-persistent-memory.html

#### Lower cost per GB than DRAM (about half [1, 2])

[1] https://www.tomshardware.com/news/intel-optane-dimm-pricing-performance,39007.html, [2] https://memory.net/memory-prices/

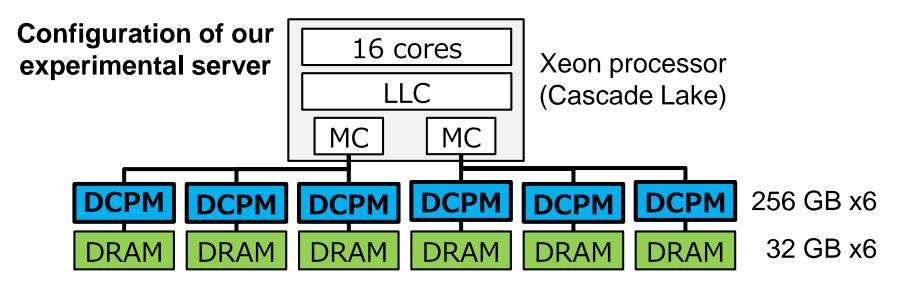

## Hybrid Memory Systems (HMS)

- Combine DRAM and DCPM to take their advantages

- DRAM is faster, but smaller and more expensive

- DCPM is larger and cheaper, but slower [Izraelevitz+, arXiv 2019]

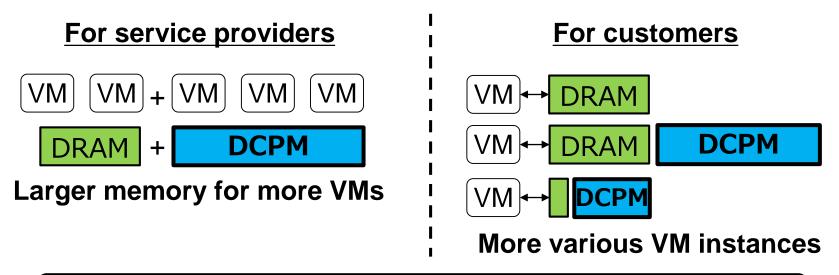

## A Use Case of HMS

Virtualization for cloud services such as IaaS

HMS will bring benefits to both service providers and customers

#### Multiple VMs are consolidated onto a single CPU

## **Executive Summary**

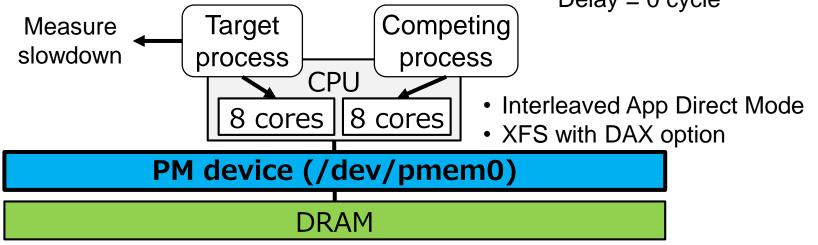

#### Objective of this work

- To analyze performance interference between two processes on a HMS (in a non-virtualized environment)

- Experimental methodology

- We co-execute *target* and *competing* processes on a single CPU

- We measure the slowdown (normalized throughput) of a target process compared to its solo execution

#### Our finding

Interference on a HMS is much different from that on a conventional DRAM-only memory system

#### **Experimental Setup**

#### 8 types of synthetic processes (Intel® Memory Latency Checker)

| Access pattern     | Sequential (Sq) or Random (Rn)         |

|--------------------|----------------------------------------|

| Read-write pattern | Read-only (R) or Read-write mixed (W2) |

| Access target      | DRAM (D) or DCPM (P)                   |

|                    | Delay = 0 cycl                         |

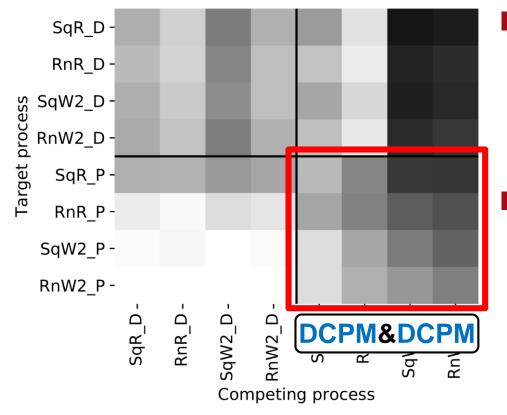

## **Slowdown of Target Process**

- 1.0 SqR\_D -RnR\_D -- 0.8 SqW2\_D -Target process - 0.6 RnW2\_D-SqR\_P-0.4 RnR P-- 0.2 SqW2 P-RnW2\_P-- 0.0 RnR\_D -SqW2\_D -SqR\_P -RnR\_P -SqW2\_P RnW2\_P. SqR\_D Competing process

■64 (= 8x8) combinations ■ Darker color  $\Rightarrow$ larger slowdown compared to solo execution

### Interference b/w Processes Accessing DRAM FUITSU

#### Interference on a DRAM-only system

Small differences between different combinations

Entirely grayed

## Interference b/w Processes Accessing DCPM Fujitsu

Similar results to "DRAM&DRAM" case

Entirely grayed

#### Some exceptions

Please refer to our paper for the details

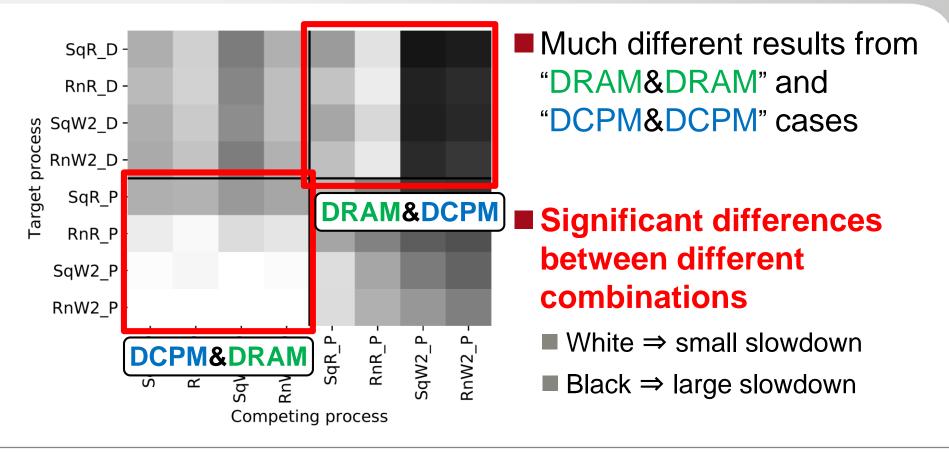

#### Interference between DRAM/DCPM Accesses Fujitsu

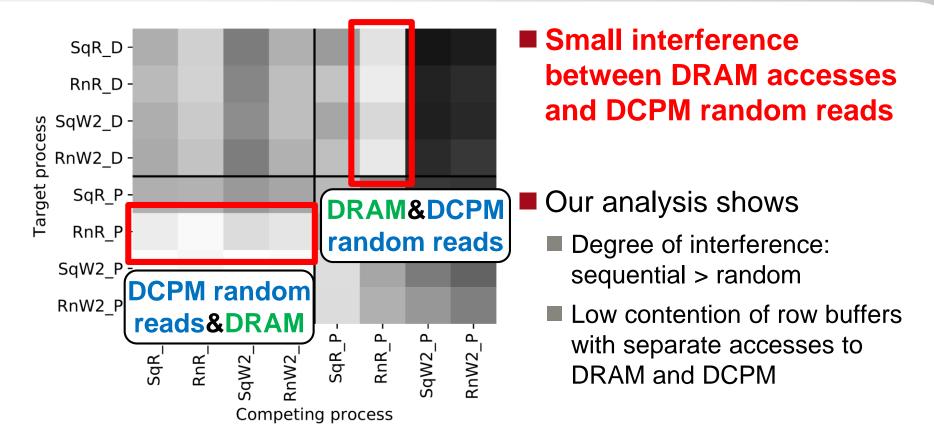

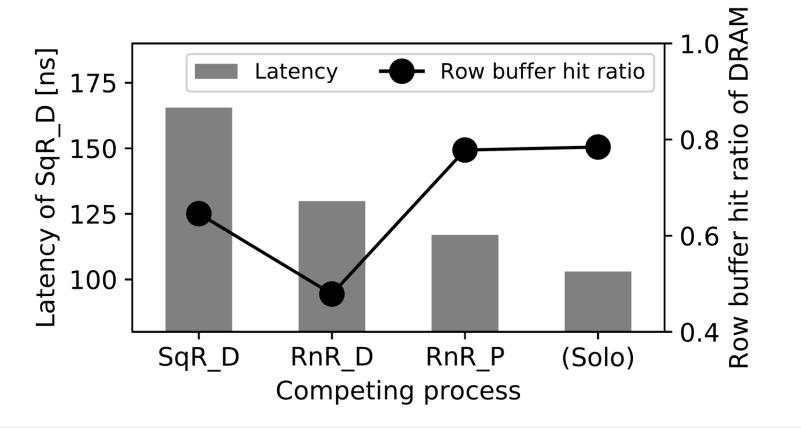

## **Observation 1: Small Interference**

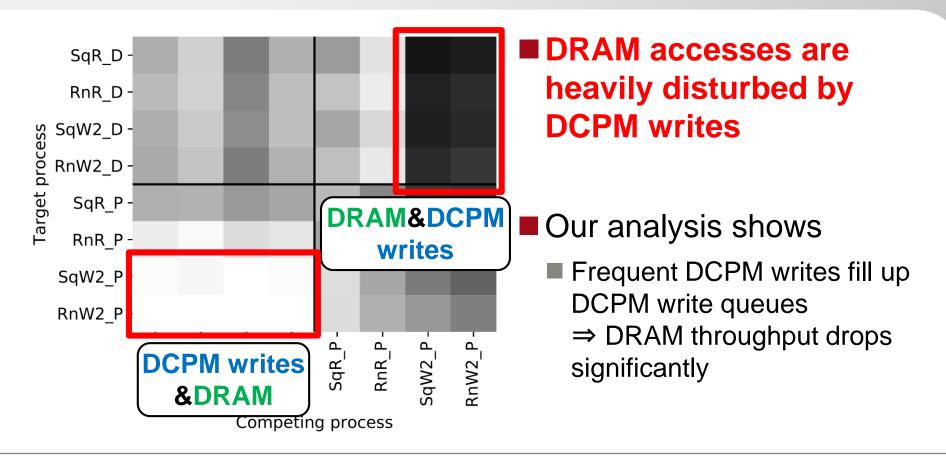

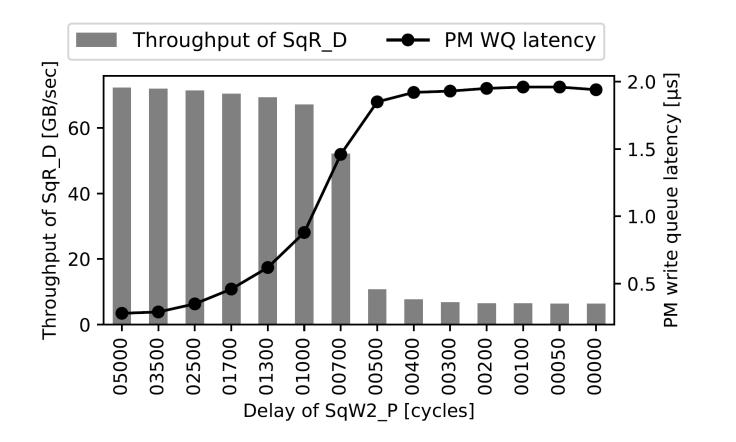

## **Observation 2: Significant Interference**

FUITSU

## Conclusion

HMS will bring benefits to could services such as IaaS

Multiple VMs are consolidated onto a single CPU

We evaluate and analyze the performance interference between two processes on a HMS

Two observations:

- Small interference between DRAM accesses and DCPM random reads

- DRAM accesses are heavily disturbed by frequent DCPM writes

# FUJITSU

shaping tomorrow with you

## Analysis of Small Interference on HMS

FUITSU

## Analysis of Significant Interference on HMS

FUÏTSU