# Intel® Xeon Phi<sup>™</sup> Processor Update

Barry Davis General Manager, Accelerated Workloads Group (AWG) Intel Data Center Group 27 September 2017

**Advancing Science**

High ROI: \$515 Return Per \$1 of HPC Invest<sup>1</sup> **Data-Driven Analytics**

### **Diverse & New Workloads Driving Science & Industry**

High Performance Data Analytics

<sup>1</sup>Source: IDC HPC and ROI Study Update (September 2015)

- HPC Market & Trends

- Yesterday and Today

- What's Next

# HPC Market & trends

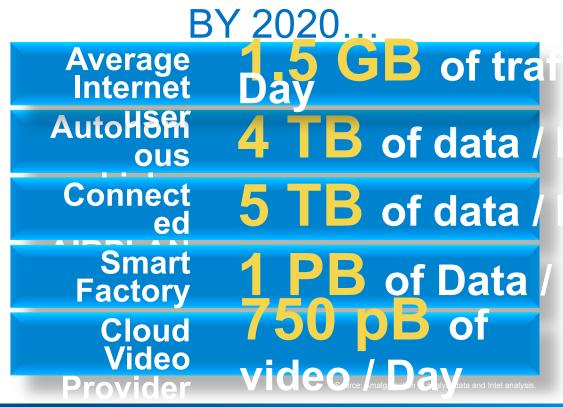

# The Coming Flood of Data (and Compute)

# 2016

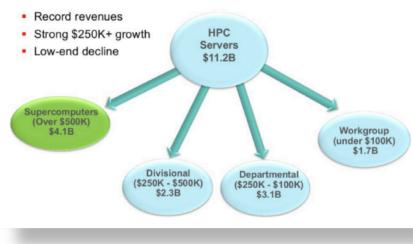

#### The Worldwide HPC Server Market: \$11.2 Billion in 2016

Source: https://www.top500.org/news/hpc-market-hits-record-revenues-in-2016-looks-ahead-to-double-digit-growth-in-ai

2021 HPC Growth to \$14.8B, \$5.4B in Supercomputing\*

**Exascale Systems**

Optimized and Efficient Processing

Distributed computing and expanding parallelism

More real-time computing and Network Bandwidth

### **HPC Trends**

# Exascale ComputingArtificial Intelligence

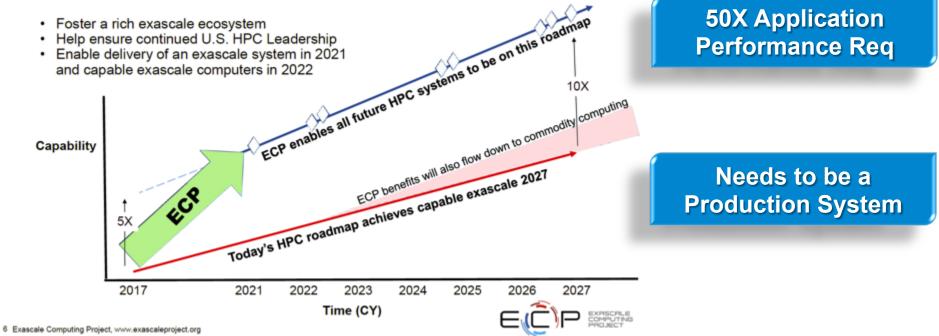

# **Thoughts on Exascale**

#### **ECP Goals**

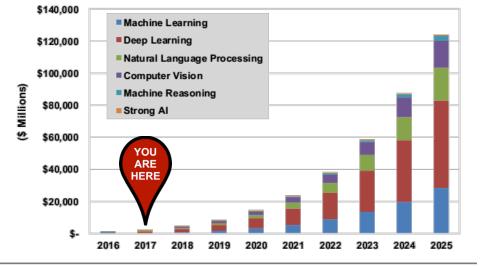

## Dawn of Artificial Intelligence

#### Chart 3.5 Annual Artificial Intelligence Revenue by Technology, World Markets: 2016-2025

(Source: Tractica)

"In the past a lot of S&P 500 CEOs wished they had started thinking sooner than they did about their Internet strategy. I think five years from now there will be a number of S&P 500 CEOs that will wish they'd started thinking earlier about their AI strategy."

> - Andrew Ng Al luminary

Quote source: http://fortune.com/ai-artificial-intelligence-deep-machine-learning/

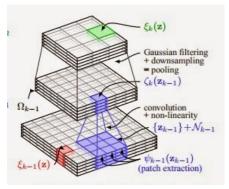

### Workflow Convergence $\rightarrow$ Simulation, Data Analytics and AI

Our customers are telling us HPC is changing.....

Clear evidence → ECP must treat Mod/Sim, AI, and Analytics as first class citizens (hardware & software)

Al has become a major consumer of computing cycles and it is expected to grow

- Compute deployment both at edge and in large cloud

- Will drive economies in fabric, compute with a large focus on power and perf/W

Convergence is happening in many areas

- Cloud management and development tools/environments

- Fabric architectures

- Frameworks/topologies

# Yesterday and today

Data Center Group

# Path to Exascale Computing

**General Purpose Hardware**

**Modern Applications**

# Stds Based Progr. Model → cores, caches, vectors

### Commercial Roadman So What Are Our Results to Date?

# Supercomputing: No Longer Restricted To A Few 'Superpowers'

### \$46 million <sup>1</sup>

In the late 1990s, the United States built ASCI Red, the first computer to break one trillion floating-point calculations per second barrier

Twenty years later, 3 Teraflops of double precision compute could be delivered in one compute node one Intel® Xeon Phi<sup>™</sup> 7200 family processor

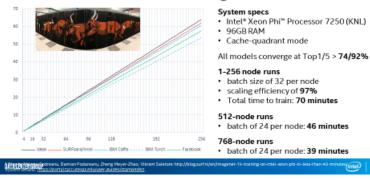

### Intel-SURFsara Research Collaboration\*

#### INTEL-SURFSARA RESEARCH COLLABORATION\*

#### **Research Goals:**

- Fastest time-to-train and time per iteration for deep neural network models

- Generalization of methodology to various Intel CPU architectures

#### Recent Breakthroughs < blog link > \*\*

- Achieving Deep Learning Training in less than 40 Minutes on ImageNet-1K

- Highest-to-date Accuracy and Training Time on ImageNet-22K and Places-365

DATA CENTERCOMPARIANTIA Codesana (PI), Ph.D.; Damian Podansana, MSc; Zheng Meyer-Zhao, MSc; SURFaata & Viknam Saletona (Co-PI), Ph.D: Intel Corp DATA CENTERCOMPARIANTI (Intel Intel Control - Intel -

#### SURFsara/Intel: Scaling beyond Imagenet-1K Industry leading accuracy on large datasets \*

Places-365

Network

WRN-50-2

Resnet-152

baseline

8 million images, 365 scene categories

Architecture: Wide Residual Networks

Global

batch

size

6720

N/A

trained in a large-scale distributed fashion

#

nodes

256

N/A

Imagenet-22K 14.2 million images; 21841 object categories

Architecture: Wide Residual Networks trained in a large-scale distributed fashion

| Network             | Global<br>batch size | # nodes | Accuracy<br>(top1/top5) |

|---------------------|----------------------|---------|-------------------------|

| Resnet-101<br>(IBM) | 5120                 | 256     | 33.8                    |

| WRN-50-2            | 7680                 | 240     | 35.97/63.87             |

| WRN-50-2            | 6400                 | 200     | 36.91/65.0<br>8         |

Auf a contra going to system configuration, refer to:

(intel) | 14

Accuracy

(top1/top5)

57.26/87.46

--/85.07

Scaling up Deep Learning on Stampede 2\* Resnet-50 on Imagenet-1K

#### Scaling up Deep Learning on MareNostrum 4\* \*\* Resnet-50 on Imagenet-1K

#### System specs

- 2S Intel<sup>®</sup> Xeon<sup>®</sup> Processor 8160 (SKX)

- 96GB RAM

All models converge at Top1/5 > 74/92%

#### 1-256 node runs

- batch size of 32 per node

- scaling efficiency of 90%

- Total time to train: 70 minutes

#### 512-node run

batch of 16 per node: 44 minutes

\*\* We acknowledge PRACE for awarding us access to resource Manihostrum 4 based in Spain at Barcelona Supercomputing Center

i District Marine Content Damin Potarean, Zheng Meyer Zhao. Visian Salesse http://biog.suf.n/en/imagenet.nik.maining.on.intel.won.phi 2025setan.40.min.net/mail

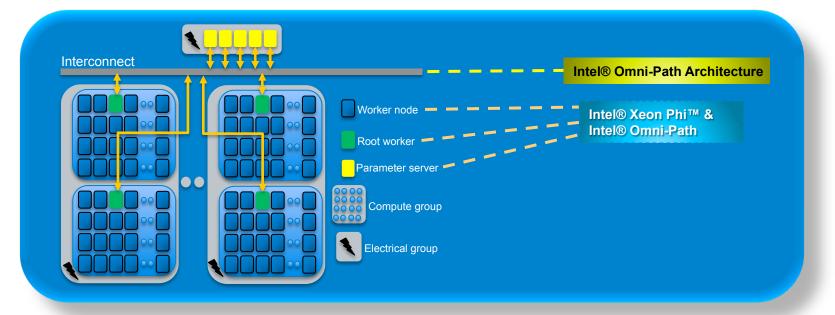

### Lawrence Berkeley National Laboratory & Stanford University

### Cori Supercomputer: First 15 Peta FLOP Deep Learning System

First 15-petaflop DL System For Solving Scientific Pattern Classification Problems On HPC Architectures

# Deep Learning at 15PF<sup>†</sup> (with NERSC, Stanford, and Univ of Montreal)

#### Scientific Achievement

- Signal vs. Background classification for LHC datasets exceeds physics cuts

- Pattern discovery for Climate data

#### **Methods Achievement**

- Hybrid parameter update strategy

- Supervised and semi-supervised architectures

#### **CS** Achievement

- IntelCaffe + MLSL optimized on KNL

- ~2TF peak on single KNL node

- ~15 PF peak on ~9300 nodes

† "Petascale Deep Learning" Thorsten Kurth, Jian Zhang, Nadathur Satish, Ioannis Mitliagkas, Evan Racah, Mostofa Patwary, Tareq Malas, Narayanan Sundaram, Wahid Bhimji, Mikhail Smorkalov, Jack Deslippe, Mikhail Shiryaev, Srinivas Sridharan, Prabhat, and Pradeep Dubey, accepted at Supercomputing 2017

### Celeste: 1st Julia application to hit 1PF<sup>†</sup> (In collaboration with NERSC, UCB, MIT and Julia Computing)

### Scientific Achievement

- First catalog with parameter & uncertainty estimates for over 300M obje

- 55 TB SDSS dataset processed in 15 minutes

- DESI instrument will use catalog for target selection

### **Methods Achievement**

- Bayesian Inference on world's largest generative model (in science)

- Joint estimation of Billions of parameters

### **CS** Achievement

- Code written in Julia, optimized for execution on KNL

- Code scaled on 9300 Cori KNL nodes

† Cataloging the Visible Universe through Bayesian Inference at Petascale in Julia; https://www.youtube.com/watch?v=uecdcADM3hY&feature=youtu.be

# Intel® Xeon Phi<sup>™</sup> Processor Top500 Listings

June 2017 Top500 List<sup>1</sup> has 13 Intel Xeon Phi deployments over 57.5 PetaFlops

Seven listings in Top 50:

**NERSC** #6: Cori (NERSC, USA); Cray XC – 14 PFs

CO JCAHPC #7: Oakforest PACS (JCAHPC, Japan); Fujitsu CX1640 M1 – 13.5 PFs TACC

#14: Marconi (CINECA, Italy); Lenovo – 6.2 PFs

#16: Theta (Argonne National Lab, USA); Cray XC40 – 5.8 PFs

#29: Onyx (ERDC DSRC, USA); Cray XC40 – 3.4 PFs

#37: Camphor 2 (ACCMS, Kyoto Univ, Japan); Cray XC40 – 3.0 PFs

nte

**XEON PH** inside

## Where Does This Leave Us?

Based on our progress ....

- Continuing to deliver better, modern code and scale application performance

- Incorporating new capabilities and technologies into the HPC Workflow

- On track for Exascale in 2021

"Now this is not the end. It is not even the beginning of the end. But it is, perhaps, the end of the beginning."

- Winston Chrchill

### We've Made Great Progress...But It's Time To Double Down!

# What's next

# Today...Highly parallel

Intel® Xeon® Processors are increasingly parallel with larger vectors...and benefits from modern code

CPU Generation (2011-2016)

Vectorized & Parallelized

Scalar & Parallelized Vectorized & Single-Threaded Scalar & Single-Threaded

Intel® Xeon Phi<sup>™</sup> Processors are extremely parallel and use general purpose programming

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more information go to http://www.intel.com/performance

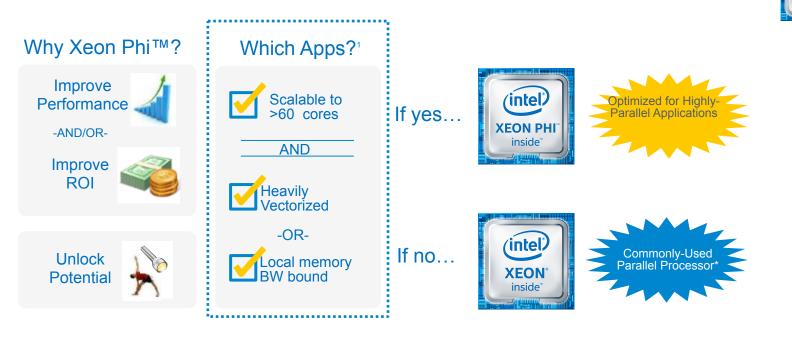

# When to Use Intel® Xeon Phi™

Intel® Xeon Phi<sup>™</sup> is optimal for applications that scale to >60 cores and are highly threaded or memory bandwidth bound

Data Center Group<sup>Performance</sup> results on Intel® Xeon Phi<sup>™</sup> will vary depending on app characteristics. For more information, see:

XEON PH inside

# Intel® Xeon® Processor Scalable Family

Sky acternance for widest variety of AI & other datacenter workloads – including deep learning

Most agile AI platform

Begin your Al journey today using existing, familiar infrastructure

- Increase datacenter utilization without additional, unique investment

- Use common AI frameworks and/or BigDL for scale deep learning training on Spark Hadoop

**Potent Performance**

inte

XFON

ATINUN inside"

Up to 2.2X deep learning training & inference perf vs. prior gen<sup>1</sup>

- ✓ More cores, threads (up to 28 & 56)

- ✓ Intel® AVX-512

- ✓ Faster I/O ✓ 6 mem channels

- ✓ INT8 support

- Optimized SW: cut training time from days to hours  $\checkmark$ with up to 113x perf vs. prior gen<sup>2</sup>

### **Production-ready**

Robust support for full range of Al deployments

- Runs all combinations of AI workloads:

- Classic ML Emerging AI

- Deep Learning Reasoning

- Analytics

- □ More

- Server-class reliability, hardware enhanced security and manageability

#### <sup>1,2</sup>Configuration details on slide: 40

Notice Revision #20110804

#### Data Center Group

23

Software and workloads used in performance tests may have been optimized for performance only on Intel microgroupsessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software and functions. And functions. And functions and performance tests may have been optimized for performance of that product known to enter product. For one complete information and performance tests may have been optimized for performance of that product known to enter product for performance tests may have been optimized for performance tests may cause the results to vary. You should consult other information and performance tests to assist you in 10th evaluating your contemplated by the performance of that product known then products. For more complete information sist, they performance tests and you of the performance of that product known then products. For more complete information was the product known to experiment in the products for the products for the products. The performance of that product known then products. For more complete information was the performance set of the performance of that product known then products. For more complete information was the performance set of the performance of that product known the products. For more complete information was the performance of the performance Optimization Notice: Intel's compilers' may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

### All purpose

#### Intel® Xeon® Processor Family **most agile Al Platform**

Scalable performance for widest variety of AI & other datacenter workloads – including deep learning training & inference Highlyparallel

Intel® Xeon Phi™ Processor (Knights Mill⁺) Faster DL Training

Scalable performance optimized for even faster deep learning training and select highly-parallel datasenter workloads\*

# Datacenter

Flexible acceleration

Intel® FPGA Enhanced DL

# Inference

Scalable acceleration for deep learning inference in real-time with higher efficiency, and wide range of workloads & configurations

Crest Family<sup>†</sup> Deep learning by design

Scalable acceleration with best performance for intensive deep learning training & inference

ights Mill (KNM); select = single-precision highly-parallel workloads generally scale to >100 threads and benefit from more vectorization, and may also benefit from greater memory bandwidth e.g. energy (reverse time migration), deep learning training, etc. products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

# What is Knights Mill?

First Intel product targeted specifically at Deep Learning training workloads

- Up to 4x DL Peak performance over Intel® Xeon Phi<sup>™</sup> Processors 7200 Series<sup>1</sup>

Built on top of 2nd generation Intel® Xeon Phi<sup>™</sup> processor

- Improved efficiency

- Optimized for scale-out

- Enhanced variable precision

- Flexible, high capacity memory

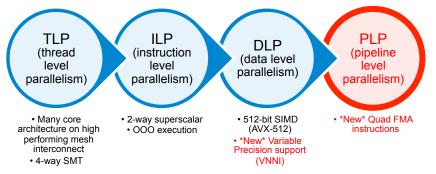

#### Knights Mill exploits 4 levels of parallelism

Intel internal estimate: Performance estimate wrt Xeon Phi™ 7290 SKU SGEMM. Performance Calculation= AVX freq X Cores X Flops per Core X Efficiency

### **Goals Moving Forward**

Hasten Pace Of Architectural Innovation And Increase Cadence Of New Products

> Deliver Improved, Real World Application Performance

Single Platform Scalable to Multiple Workloads – Mod/Sim, AI (Machine & Deep Learning), Analytics → On-prem and in the Cloud

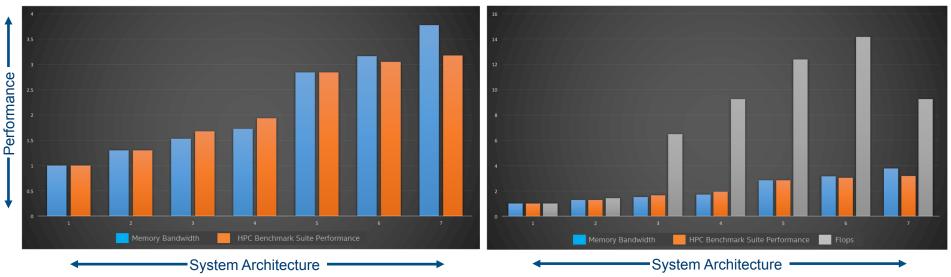

# Some Food For Thought Application Performance: Memory BW vs FLOPS

Application Performance: Memory BW

Application Performance: FLOPS

### **Application Performance comes from Memory BW not FLOPS**

Source: Supercomputing OEM

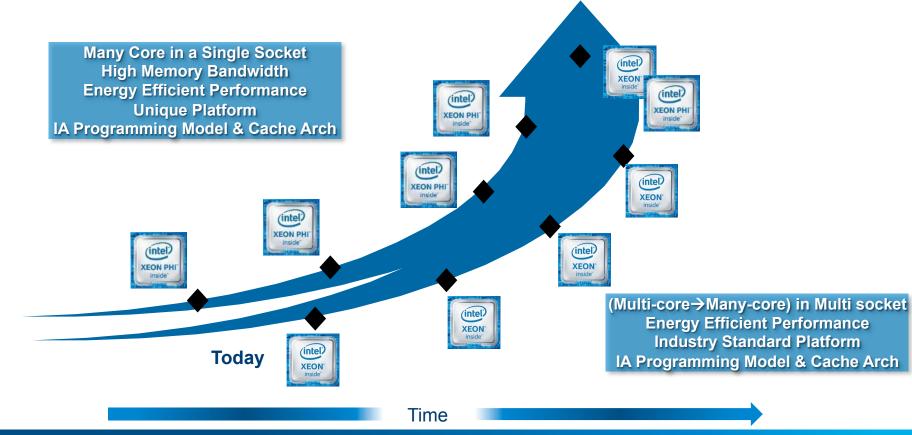

# **Prior Direction**

# **Today's Direction**

(Multi-core→Many-core) in Multi socket Energy Efficient Performance Industry Standard Platform IA Programming Model & Cache Arch High Memory Bandwidth Parallel Workload Optimizations

intel

**XEON PH**

inside

intel

**XEON PHI**

(intel)

XEON

Today

XEON

(intel

**XEON PH**

inside

(intel)

XEON inside

(intel) XEON' inside

Time

XEON PH

XEON PH

# Shameless advertisements

### KNL Developer Program: XeonPhiDeveloper.com

Order your turnkey Intel® Xeon Phi<sup>™</sup> Platform today! Cutting edge platform capabilities, performance to deliver multithreaded, vectorized software for today's HPC workloads!

#### Data Center Group

\*Names and brands may be claimed as the property of others

#### \*Names and brands may be claimed as the property of others

## Intel® Xeon Phi: Remote Access Worldwide

- Try open, broad remote access to Intel® Xeon Phi<sup>™</sup> processor based platforms for free (limited time) from our worldwide partners

- Cluster includes Intel Parallel Studio XE Cluster Edition, Intel Omni-Path Architecture and Intel SSDs

- Utilize key workloads/ benchmarks or bring your code

- Test scalability beyond single node

- Try before you buy!

### Dell\*: Click <u>here</u> to access

| •                  |                                                                                                                                                       |                                                                                                                                               |         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                    |                                                                                                                                                       | Complete the form below to have a sales<br>expert contact you.<br>If Looking for technical apport if at the life tags.<br>Rest Name Last Name |         |

|                    |                                                                                                                                                       | Business Email                                                                                                                                | Company |

|                    |                                                                                                                                                       | Best Plane                                                                                                                                    | City .  |

|                    |                                                                                                                                                       | e g xononox<br>Address                                                                                                                        | Cly     |

| Remote Access to I | ntel® Xeon Phi <sup>™</sup> Processors                                                                                                                | Address                                                                                                                                       |         |

| DALLENC            | Dell EMC's remote access program allows you to<br>evaluate and optimize your own code, and to test<br>computational applications optimized for intel® | Country                                                                                                                                       |         |

| NUTANK             | architecture, on systems based on Intel® Xeon Phi <sup>®</sup>                                                                                        | United States                                                                                                                                 |         |

Data Center Group

### Penguin\*: Click

Fujitsu\*: Click

# Colfax\*: Click

### Rescale\*: Click

|                                                                                                                 | Fmail                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| The second se | Enai                                                                                                                             |

| rescale (intel)                                                                                                 | Paceword *                                                                                                                       |

|                                                                                                                 | Password                                                                                                                         |

|                                                                                                                 | Name 1                                                                                                                           |

|                                                                                                                 | Name                                                                                                                             |

| iting with Intel and RSystems to<br>Phy Cloud with Omni Path                                                    | Phone                                                                                                                            |

| ged by R Systems, the Xeon Phi                                                                                  | Phone                                                                                                                            |

| erformance gains of intells<br>cessors with Ormal Path directly                                                 | Company                                                                                                                          |

| ientists through Rescale's cloud                                                                                | Company                                                                                                                          |

| n.                                                                                                              |                                                                                                                                  |

| loud you pet                                                                                                    | Role                                                                                                                             |

| we computing on ScaleX Pro                                                                                      | Specify Your Role •                                                                                                              |

| ism and vectorization delivered                                                                                 | I agree to the Terms & Conditions                                                                                                |

| i processors                                                                                                    | By providing your context information, you are confirming you are                                                                |

| fabric with Intel Omni-Path                                                                                     | an adult 18 years or older and you authorize strar and/or Rescale to                                                             |

| lecture                                                                                                         | contact you by email or telephone with information about intel<br>and to Bearair conducts, quests, and undates for arthubur and  |

| and optimized codes on Intel                                                                                    | business professionals. You may unsubscribe at any time by                                                                       |

| 6915                                                                                                            | clicking the link provided in our communications. Please review<br>profits Private Native and Terms of Use for more effortation. |

| job management and                                                                                              | Index Privacy Nation and Terms of Dar for more afformation.                                                                      |

|                                                                                                                 |                                                                                                                                  |

| transfer and encryption at rest                                                                                 | Sf Sign Up                                                                                                                       |

| IcaleX Developer                                                                                                |                                                                                                                                  |

|                                                                                                                 |                                                                                                                                  |

Email address

ROSTENS

Four weeks of fr

Massive parallel by Intel Xeon Ph

Optimized HPC1 integrated archit

Pre-configured a Xeon Phi proces

Instative GUI for collaboration

Secure SSL data

Beta access to 5

Go to www.remotexeonphi.com – Portal with multiple partners. Free (limited time), broad and open access for developers and customers

(intel)

**XEON PHI**

#### Key Topics:

- Parallel Programming

- High Productivity Languages

- Artificial Intelligence

- Systems

- Enterprise

- Visualization Development

#### **All Technical Content:**

- 77 Lectures (30 minutes)

- **15** Tutorials (90 minutes)

- 30 Poster Chats (60 minutes)

### Register Now! intel.com/hpcdevcon

# In Summary .....

### Delivering Exascale and Mainstream Performance in a Common Investment

Industry Leading Platform Features and Architectural Capabilities

Common SW Architecture and Programming Model  $\rightarrow$  Always

Consistent Workload Tuning and Modernization Techniques  $\rightarrow$  Always

Common platform for All Workloads → Mod/ Sim, Al, Analytics

### Improving Data Visualization with Intel® Solutions

Optimizing for Visualization Optimized for parallel processing and latest instruction sets OpenSWR\*, Embree\*, & OSPRay\* all available Used by ParaView\*, VisIt\*, VMD\*, CEI\* EnSight\*, and more...

Reducing Cost for Visualization Lower cost of host vs cost of host + card for GPUs Single host can address up to 384GB memory Additional use as general purpose compute platform

Pre-Configured Appliance Solution Available Now 1.58x to 1.91x better performance than GPUs<sup>1</sup> Supports data sets up to 1.5TB Standard configuration price \$79,000<sup>2</sup> More Info: <u>http://sdvis.xeonphi.com/</u>

#### For in-situ, post-processing, and professional rendering visualization needs

\*Other names and brands may be claimed as the property of others.

<sup>2</sup>Pricing as of June 15, 2017. Pricing is subject to change without notice

1Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer sys at an one of the second state of

(intel

### Configuration details 64-node CPU system Intel® Xeon® 6148 Gold processor with 10GB Ethernet

MLSL Library version

MKL Library version

MKL DNN Library

Version

| Benchmark Segment    | AI/ML                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------|

| Benchmark type       | Training                                                                                           |

| Benchmark Metric     | Images/Sec or Time to train in seconds                                                             |

| Framework            | Caffe                                                                                              |

| Тороlоду             | Resnet                                                                                             |

| # of Nodes           | 64                                                                                                 |

| Platform             | Wolfpass (Skylake)                                                                                 |

| Sockets              | 2S                                                                                                 |

| Processor            | Xeon Processor code named Skylake, B0, ES2*,<br>24c, 2.4GHz, 145W, 2666MT/s, QL1K<br>CPUID=0x50652 |

| BIOS                 | SE5C620.86B.01.00.0412.020920172159                                                                |

| Enabled Cores        | 24 cores / socket                                                                                  |

| Platform             | Wolfpass (Skylake)                                                                                 |

| Slots                | 12                                                                                                 |

| Total Memory         | 192GB                                                                                              |

| Memory Configuration | 12x16GB DDR4 2R, 1.2V, RDIMM, 2666MT/s                                                             |

| Memory Comments      | Micron MTA 18ASF2G72PDZ-2G6B1                                                                      |

| SSD                  | 800GB Model: ATA INTEL SSDSC2BA80 (scsi)                                                           |

| OS                   | Oracle Linux Server 7.3, Linux kernel 3.10.0-514.6.2.0.1.el7.x86_64.knl1                           |

|                      |                                                                                                    |

| Other Configurations | Intel Corporation Ethernet Connection X722 for<br>10GBASE-T (rev 03)                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------|

| HT                   | ON                                                                                                               |

| Turbo                | ON                                                                                                               |

| Computer Type        | Server                                                                                                           |

| Framework Version    | https://github.com/intel/caffe<br>Release 1.0.3                                                                  |

| Topology Version     | ResNet-50 Facebook variant, refer to<br>models/intel_optimized_models/multinode/<br>resnet_50_256_nodes_8k_batch |

| Dataset, version     | Imagenet, ILSVRC 2012 (/lfs/lfs09/<br>Imdb_raw_compressed)                                                       |

| Performance command  | d caffe train -solver solver.prototxt -engine MKLDNN                                                             |

| Data setup           | Convert to LMDB from raw ILSVRC 2012 images                                                                      |

| Compiler             | gcc 4.8.5 20150623                                                                                               |

| MPI Library version  | Version 2017 Update 3 Build 20170405                                                                             |

mklml Inx 2018.0.20170720

v0.9.0

f068d07deccf175a0bc8fe51f0eedce37a2a4470

37

### **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL® PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. Roadmap not reflective of exact launch granularity and timing – please refer to ILU guidance. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Any code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families: Go to: Learn About Intel® Processor Numbers

All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice. Material in this presentation is intended as product positioning and not approved end user messaging.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. Check with your system manufacturer or retailer or learn more at <u>www.intel.com</u>.

Intel, Intel Inside, the Intel logo, Xeon and Xeon Phi are trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2017, Intel Corporation

\*Other names and brands may be claimed as the property of others

# Legal Disclaimer & Optimization Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Copyright© 2017, Intel Corporation. All rights reserved. Intel, the Intel logo, Atom, Xeon, Xeon Phi, Core, VTune, and Cilk are trademarks of Intel Corporation in the U.S. and other countries.

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804