# Tools, Standards and Books, oh my! Compilers, libraries and VTune™, oh my!

James Reinders and Thanh Phung, Intel July 8, 2014; IXPUG; Austin, TX

Thank you for being a part of this Intel® Xeon Phi™ Users Group.

## Neo-Heterogeneous

the compared to the control the control to the cont

It's a lot more to us than a cute marketing phrase.

It started as a technical concept, and remains one for us *all*.

## It's the Programming Model, Stupid.

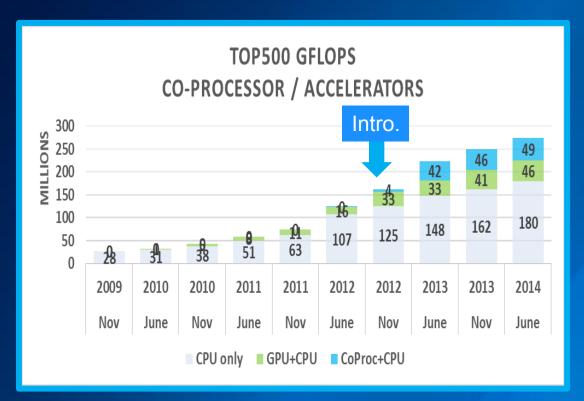

#### June 2014 Top 500 List

#1 system (third time)

Neo-heterogeneous

(Intel® Xeon® Processors + Intel® Xeon Phi™ Coprocessor)

Common

Programming

Model

- Knights Landing

- Programming Standards and their growth/evolution

- Intel Parallel Computing Centers (IPCCs)

- Education: course work

#### **Knights Landing**

(Next Generation Intel® Xeon Phi™ Products)

Platform Memory: DDR4 Bandwidth and Capacity Comparable to Intel® Xeon® Processors

Intel® Silvermont Arch. Enhanced for HPC

**Integrated Fabric**

**Processor Package**

Conceptual—Not Actual Package Lavou

Continued programming model advantag Add Intel® AVX-512 instructions gcc work well underway

#### Compute: Energy-efficient IA cores

- Microarchitecture enhanced for HPC

- 3X Single Thread Performance vs Knights Corner

- Intel Xeon Processor Binary Compatible

#### On-Package Memory:

up to **16GB** at launch

■ **1/3X** the Space

**5X** Bandwidth vs DDR4

■ **5X** Power Efficiency

Jointly Developed with Micron Technology

- Knights Landing

- Programming Standards and their growth/evolution

- Intel Parallel Computing (Latest Intel tools in beta (2015)

Education: course work OpenMP\* 4.0 support **Explicit Vectorization**

(see my SGIUG talk – lotsofcores.com) A talk about the need for explicit vectorization, given at SGIUG on April 30, 2014

- Knights Landing

- Programming Standards and their growth/evolution

- Intel Parallel Computing Centers (IPCCs)

- Education: course work

SeisSol. **ROTOR** Quantum Optimized OPENMP/ **AMBER VASP** UTBENCH SU<sub>2</sub> SG++ Openflow **NWChem** WRF VISIT SIM integral GADGET. **AVBP** Announcing new mailing list: http://tinyurl.com/IPCCmaillist NEMO5 (Large New IPCCs being added (rolling basis) Eddy) **MPAS** Watch for University of Oregon developed 4/500 level curriculum Blast Intel® Parallel Computing Centers Mardyn **BUDE MACPO** CERF/C University of CAM-5 🐸 BRISTÓL ETH zürich **CASTEP** Harmonie Castep **GTC** 📑 🏍 UNIVERSITY 🗗 OKLAHOMA THE UNIVERSITY **CESM** GS2 Stanford University University of Colorado Boulder CFSv2 Gromacs **GPAW** CIRCAC BERKELEY LA

CliPhi (COSMOS)

COSA

Cosmos codes

DL-MESO

DL-Poly

ECHAM6

Elmer

FrontFlow/Blue Code

**GADGET**

**GAMESS-US**

\*Other brands and names are the property of their respective owners.

- Knights Landing

- Programming Standards and their growth/evolution

- Intel Parallel Computing Centers (IPCCs)

- Education: course work

Intel® Xeon Phi™ Coprocessor High-Performance Programming, 2013

Multithreading for Visual Effects, 2014 (June)

User driven – contribution based books on parallel programming - "inspired by the highly scalable Intel®

### High Performance Parallelism Pearls – Successful Approaches for Multicore and Many-core Pregramming es.com/gems

#### Status:

- Volume 1 DEFINITELY HAPPENING being written/edited, target availability end of 2014

- Volume 2 PLANNED (assume volume 1 is a "hit") submissions being accepted (writing due end of 2014), publish in 2015 submit your proposal now: http://lotsofcores.com/gems

Software

#### Legal Disclaimer & Optimization Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Copyright © 2014, Intel Corporation. All rights reserved. Intel, Pentium, Xeon, Xeon Phi, Core, VTune, Cilk, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804